|

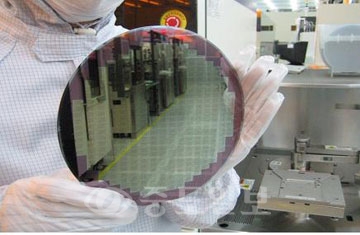

| ▲ 3차원 집적회로 웨이퍼(집적 회로를 만들 때 쓰는 직경 5~10cm의 실리콘 단결정의 얇은 판). |

교육과학기술부는 대전 소재 나노종합팹센터(소장 이희철)와 미국 벤처기업 비상(사장 이상윤), 스탠포드나노팹(소장 요시오 니시) 등 3개 기관 공동으로 이 같은 기술개발에 성공했다고 17일 밝혔다.

지난해 초 스탠포드나노팹에서 0.8㎛급 4인치 웨이퍼에서 10kb 기술이 구현된 이후, 같은 해 7월부터는 국내의 나노종합팹센터에서 180nm급 8인치 웨이퍼에서 상용화가 가능한 128Mb 기술개발로 이어졌다.

미국 벤처기업 비상은 이번 기술을 사용해 2009년부터 시장진입을 준비하고 있다.

구현방식을 보면, 업계 표준인 180nm급 CMOS 기술과 8인치 실리콘 반도체 웨이퍼를 이용해 구현한 것으로, 전 공정이 섭씨 400도 이하의 저온공정으로 진행됐다.

또 금속배선층을 포함하는 실리콘 반도체 기판 상에 서브마이크론(1㎛ 미만)의 두께를 가진 단결정 실리콘층을 형성한 후 고성능의 신뢰성 높은 반도체 소자를 형성함으로써, 단일칩 3차원 집적회로 구현을 가능케 했다.

이밖에 기존의 비아 컨텍기술을 이용해 무한대의 3차원 중간배선을 가능하게 했다.

기존의 2차원적 반도체 제조기술의 경우 해가 갈수록 비용 증가와 기술적인 난제 등의 어려움에 직면해 왔다.

전 세계 관련 연구기관들도 이 점을 감안해 지난 수십년간 3차원 반도체 제조기술 구현에 많은 시간과 노력을 투자했지만, 고온의 제조공정과 반도체 층간에서 발생하는 결함, 제한적인 배선 개수 등은 또 하나의 난제로 작용했다.

이번에 개발된 3차원 집적회로 탄생의 의미를 잘 보여주는 것으로, 향후 수 세대에 걸친 기술활용이 가능하고 동일 웨이퍼 면적에서 더 많은 반도체 칩 생산이 가능해지면서 반도체 생산비용을 획기적으로 낮출 것으로 기대된다.

이희철 나노종합팹센터 소장은 “이번 기술개발은 나노종합팹센터가 보유한 첨단 기술을 활용해 새로운 반도체 기술을 상용화했다는 점에서는 의미가 크다”며 “향후 반도체 산업 분야에서 초저가 생산 단가 및 고성능 반도체 솔루션 제공이 가능할 것으로 보인다”고 말했다./이희택 기자

중도일보(www.joongdo.co.kr), 무단전재 및 수집, 재배포 금지

이희택 기자

이희택 기자

![[尹정부 반환점 리포트] ⑪ 충북 현안 핵심사업 미온적](https://dn.joongdo.co.kr/mnt/webdata/content/2024y/11m/21d/118_2024112101001603200062341.jpg)

![[기획]`대한민국의 스페이스X를 꿈꾼다`... 페리지에어로스페이스의 도전](https://dn.joongdo.co.kr/mnt/webdata/content/2024y/11m/20d/78_2024112001001447200056411.jpg)